Учебно-лабораторный стенд «Программируемые логические интегральные схемы» ПЛИС

Артикул: УП-1071 Цена: предоставляется по запросу |

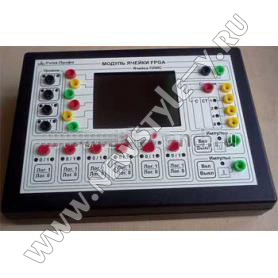

На сегодняшний день микроконтроллерная и микропроцессорная техника представляет собой одно из самых бурно развивающихся направлений в электронике. Если в конце XX века для реализации какого-либо сложного устройства требовалась, как минимум, дюжина микросхем, то на сегодняшний день дискретная логика почти повсеместно вытесняется микроконтроллерами и программируемыми логическими интегральными схемами (ПЛИС). Микроконтроллер, как правило, представляет собой совокупность микропроцессора, оперативной и постоянной памяти, а также набора периферийных устройств. Работа микроконтроллера аналогична компьютеру: он выполняет заданную программистом последовательность инструкций. В ПЛИС же используется принципиально другой подход: микросхема состоит из множества разрозненных ячеек, каждая из которых может выполнять некоторые логические и арифметические функции. При программировании такой микросхемы ячейки соединяются между собой заданным образом, синтезируя целостную схему из ячеек. Таким образом, микросхему ПЛИС можно представить как множество логических элементов, которые можно произвольно соединять между собой. Используются ПЛИС в задачах, где требуется высокая скорость обработки данных (к примеру, обработка видеосигналов), требуется одновременная работа нескольких независимых узлов (например, система управления инжекторным двигателем внутреннего сгорания) и другие применения. В некоторых современных ПЛИС количество встроенных логических ячеек настолько велико, что позволяет реализовывать даже несложные микроконтроллерные системы. Модуль ячейки FPGA позволяет изучить основы функционирования логических блоков ПЛИС и их конфигурирования. Данный макет предполагает формирование студентом логической или арифметико-логической функции средствами одного гипотетического логического блока. Вторым модулем стенда является отладочный модуль FPGA, который содержит реальную микросхему фирмы Altera (семейство Cyclone IV), средства отладки и программирования, а также набор периферийных устройств. Для наглядности в этом описании размещена только лицевая панель этого модуля.

Существует две комплектации поставки: Первая включает: Состав:

Вторая включает:

Исполнение стендовое компьютерное:

Состав:

Дополнительно есть возможность заказать : Ноутбук или ПК (на выбор) и Компактный осциллограф.

Лабораторные работы.

Ниже приведены типовые лабораторные работы, которые можно провести на стендах (все работы рассмотрены в методическом пособии):

← Назад |

- Промышленная автоматика

- Системы автоматизации и промышленные сети

- Релейно-контакторные схемы управления

- Автоматизированные линии

- Лаборатории

- Стенды «Средства автоматизации и управления» (САУ)

- Лабораторные комплексы

- Автоматизация и автоматика

- Стенды «Элементы систем автоматики»

- Стенды «Промышленные программируемые контроллеры»

- Демонстрационные комплексы «Автоматизация и управление производством»

- Комплекты типового лабораторного оборудования

- Лабораторные стенды